High throughput data and signal processing applications can be specified preferably by dataflow networks, as these naturally allow the exploitation of parallelism as well globally (at the level of a network of communicating actors) as locally at the actor level, e.g., by implementing each actor as a hardware circuit. Today, there exist a few system-level design approaches to aid an algorithm designer in compiling a dataflow network to a set of processors or, alternatively, to synthesize the network directly in hardware for achieving high processing speeds. But embedded systems, particularly in the context of IoT applications, have additional requirements: Safe operation, even in an environment of intermittent power shortages, and in general (ultra-)low power requirements. Altogether, these requirements seem to be contradictory.

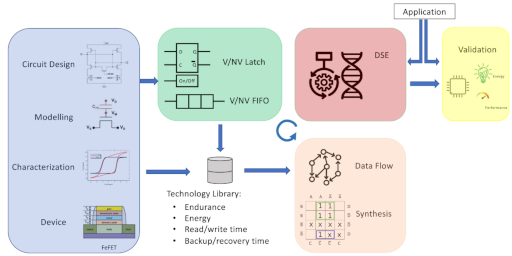

Our proposed project named HiLoDa (High performance, (ultra-Low) power Dataflow) Nets attacks this obvious discrepancy and conflict in requirements by a) introducing, exploiting, and integrating for the first time emerging FeFET technology for the design of actor networks, i.e., by investigating and designing persistable FIFO-based memory units. b) In particular, circuit devices being able to operate in mixed volatile/non-volatile mode of operation shall be modeled, characterized, and designed. c) By combining the system-level concept of dataflow, which is based on self-scheduled activations of computations with emerging CMOS-compatible FeFET technology, inactive actors or even subnets shall inherit the capability of self-powering (down and wakeup). In addition, for a continuously safe mode of operation, a down-powering must also be triggered upon any intermittent shortage of power supply. Analogously, actors shall perform an auto-wakeup after recovery from a power shortage but also subject to fireability.

HiLoDa Nets will be able to combine high clock-speed data processing of each synthesized actor circuit in power-on mode and automatic state retention using FeFET technology in power-off mode, self-triggered during time intervals of either data unavailability or power shortage. d) A fully automatic cross-layer synthesis from system-level dataflow specification to optimized circuit implementation involving FeFET devices shall be developed. This includes e) the DSE (design space exploration) of actor clusterings at the system level to explore individual power domains for the optimization of throughput, circuit cost, energy savings, and endurance. Finally, f) HiLoDa Nets shall be compared to conventional CMOS technology implementations with respect to energy consumption for applications such as spiking neural networks. Likewise, shutdown (backup) and recovery latencies from power shortages shall be evaluated and optimized.

HiLoDa Nets – cross-layer hardware synthesis design flow

Publikationen

2025

- , , , , , , :

Non-Volatile Ferroelectric-AND (FeAND) Memory Cell Design

IFIP/IEEE International Conference on Very Large Scale Integration (VLSI-SoC 2025) (Puerto Varas, 12. October 2025 - 15. October 2025)

BibTeX: Download - , , , , , , , :

FeMFET-based High Performance, Ultra-Low Power Memory Cells for Reliable State Retention of Dataflow Networks

38th IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems; Special Session (Barcelona, Spain, 21. October 2025 - 23. October 2025)

In: Proceedings of the 38th IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems 2025

BibTeX: Download - , , :

Exploration of Clock and Power Gating Tradeoffs for the Design of Self-Powering Dataflow Networks

28. Workshop Methoden und Beschreibungssprachen zur Modellierung und Verifikation von Schaltungen und Systemen (MBMV) (Rostock Warnemünde, 11. March 2025 - 12. March 2025)

In: VDE ITG; VDE/VDI GMM; GI (ed.): Proceedings of the 28th Workshop Methoden und Beschreibungssprachen zur Modellierung und Verifikation von Schaltungen und Systemen, Berlin - Offenbach: 2025

BibTeX: Download

2024

- , , , :

Self-Powering Dataflow Networks – Concepts and Implementation

22nd ACM-IEEE International Symposium on Formal Methods and Models for System Design (MEMOCODE) (Raleigh, NC, 3. October 2024 - 4. October 2024)

In: Proceedings of the 22nd ACM-IEEE International Symposium on Formal Methods and Models for System Design (MEMOCODE) 2024

DOI: 10.1109/MEMOCODE63347.2024.00013

BibTeX: Download - :

Techniques for Efficient Performance Analysis and Memory Optimization in Mapping Dataflow Models of Computation onto Embedded Systems (Dissertation, 2024)

DOI: 10.25593/open-fau-1040

URL: https://open.fau.de/handle/openfau/31834

BibTeX: Download - , , :

Exploring Multi-Reader Buffers and Channel Placement during Dataflow Network Mapping to Heterogeneous Many-core Systems

In: IEEE Access 12 (2024), p. 39748-39769

ISSN: 2169-3536

DOI: 10.1109/ACCESS.2024.3375079

BibTeX: Download

2023

- , , , , , , , , , , , , , , , :

Special Session - Non-Volatile Memories: Challenges and Opportunities for Embedded System Architectures with Focus on Machine Learning Applications

International Conference on Compilers, Architectures, and Synthesis for Embedded Systems (CASES) (HAMBURG, 18. September 2023 - 20. September 2023)

In: Proceedings of the International Conference on Compilers, Architectures, and Synthesis for Embedded Systems (CASES) 2023

BibTeX: Download

Contact

Dr.-Ing. Joachim Falk

- Phone number: +49 9131 85-25143

- Email: joachim.falk@fau.de

Prof. Dr.-Ing. Jürgen Teich

- Phone number: +49 9131 85-25150

- Email: juergen.teich@fau.de